用以太網(wǎng) Ping的方式對(duì) MAX10 FPGA 開(kāi)發(fā)套件進(jìn)行測(cè)試

對(duì)MAX10 FPGA 開(kāi)發(fā)套件進(jìn)行以太網(wǎng) Ping 測(cè)試

采用 FPGA DIY 開(kāi)發(fā)板設(shè)計(jì)一個(gè)模為60的計(jì)數(shù)器

設(shè)計(jì)一個(gè)摸為60的計(jì)數(shù)器,計(jì)數(shù)結(jié)果動(dòng)態(tài)顯示在兩個(gè)數(shù)碼管上

利用FPGA DIY開(kāi)發(fā)板實(shí)現(xiàn)數(shù)字時(shí)鐘數(shù)碼管顯示

本視頻展示的是用Verilog硬件描述語(yǔ)言設(shè)計(jì)的一個(gè)具有時(shí)、分、秒計(jì)數(shù)顯示功能,以24小時(shí)循環(huán)計(jì)時(shí)的....

在設(shè)計(jì)商店中找到MAX 10產(chǎn)品系列的參考設(shè)計(jì)的操作

通過(guò)我們的設(shè)計(jì)商店找到MAX 10產(chǎn)品系列的參考設(shè)計(jì)

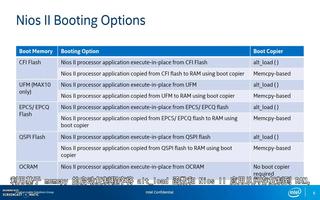

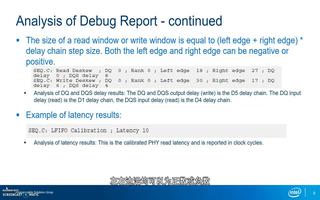

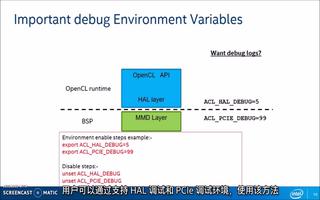

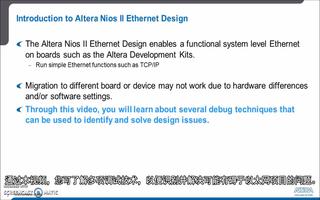

關(guān)于Nios II 以太網(wǎng)設(shè)計(jì)的調(diào)試技術(shù)(1)

Nios II 以太網(wǎng)設(shè)計(jì)的調(diào)試技術(shù) Part 1

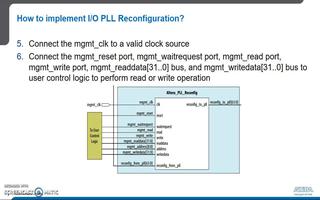

用戶(hù)模式執(zhí)行 Stratix 10 設(shè)備 IOPLL 校準(zhǔn)的方法步驟

如何以用戶(hù)模式執(zhí)行 Stratix 10 設(shè)備 IOPLL 校準(zhǔn)

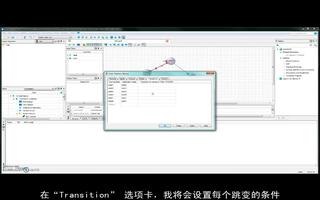

簡(jiǎn)述使用QII狀態(tài)機(jī)向?qū)绾蝿?chuàng)建一個(gè)狀態(tài)機(jī)

如何使用QII狀態(tài)機(jī)向?qū)?chuàng)建一個(gè)狀態(tài)機(jī)