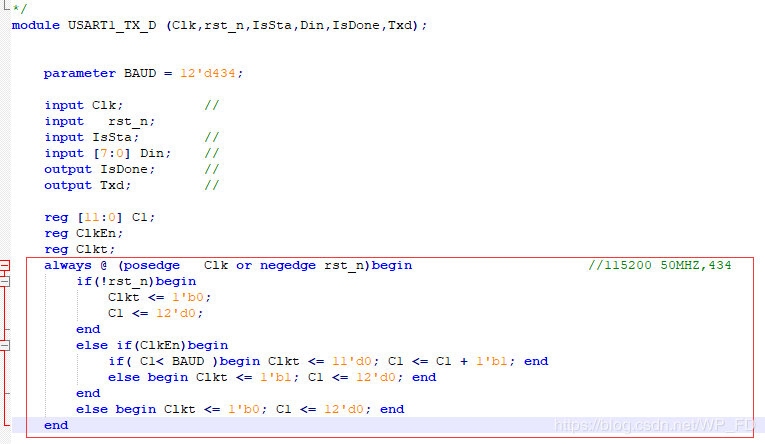

/* 計數(shù)模塊 */

always @(posedge clk1x or posedge rst or negedge clk1x_enable)

if (rst)

no_bits_sent = 4'b0000 ;

else if (!clk1x_enable)

no_bits_sent = 4'b0000 ;

else

no_bits_sent = no_bits_sent + 1 ;

/*

發(fā)送模塊

*/

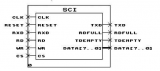

reg [7:0] tsr ; /*發(fā)送移位寄存器*/

reg parity ;

/* 校驗位 */

always @(negedge clk1x or posedge rst)

if (rst)

begin

sdo <= 1'b1 ;

tsre <= 1'b1 ;

parity <= 1'b1 ;

tsr <= 8'b0 ;

end

else

begin

if (no_bits_sent == 4'b0001)

begin

tsr <= tbr ;

//將緩沖區(qū)中的數(shù)據(jù)載入到移位寄存器

tsre <= 1'b0 ;

end

/*start bit*/

else if (no_bits_sent == 4'b0010)

begin

sdo <= 1'b0 ;

end

/*Data bits */

else if ((no_bits_sent >= 4'b0011) && (no_bits_sent <= 4'b1010))

begin

tsr[7:1] <= tsr[6:0] ;

sr[0] <= 1'b0 ;

sdo <= tsr[7] ;

parity <= parity ^ tsr[7] ;

end

/* 校驗位 */

else if (no_bits_sent == 4'b1011)

begin

sdo <= parity ;

end

else if (no_bits_sent == 4'b1100)

begin

sdo <= 1'b1 ;

tsre <= 1'b1 ;

end

end

電子發(fā)燒友App

電子發(fā)燒友App

評論